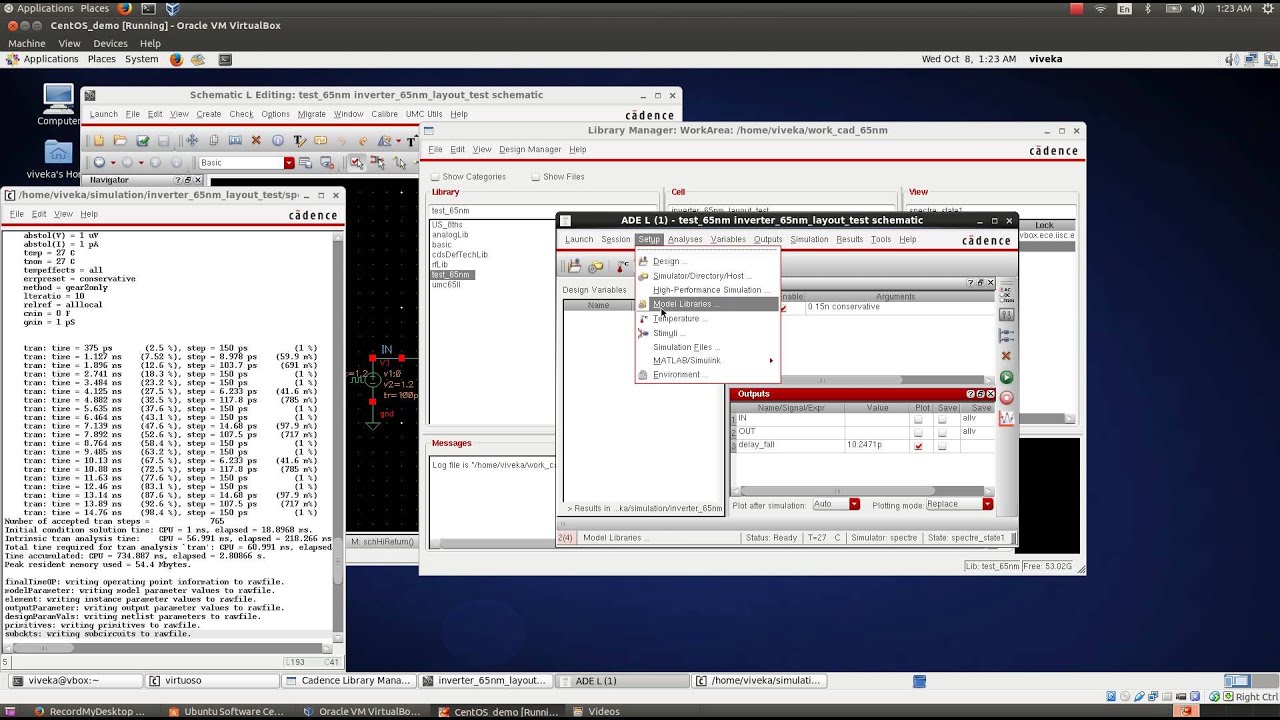

Cadence virtuoso – schematic & simulations – inverter (65nm) Using the models Ee5323 vlsi design i using cadence

Cadence Virtuoso – Schematic & Simulations – Inverter (65nm) | Sudip

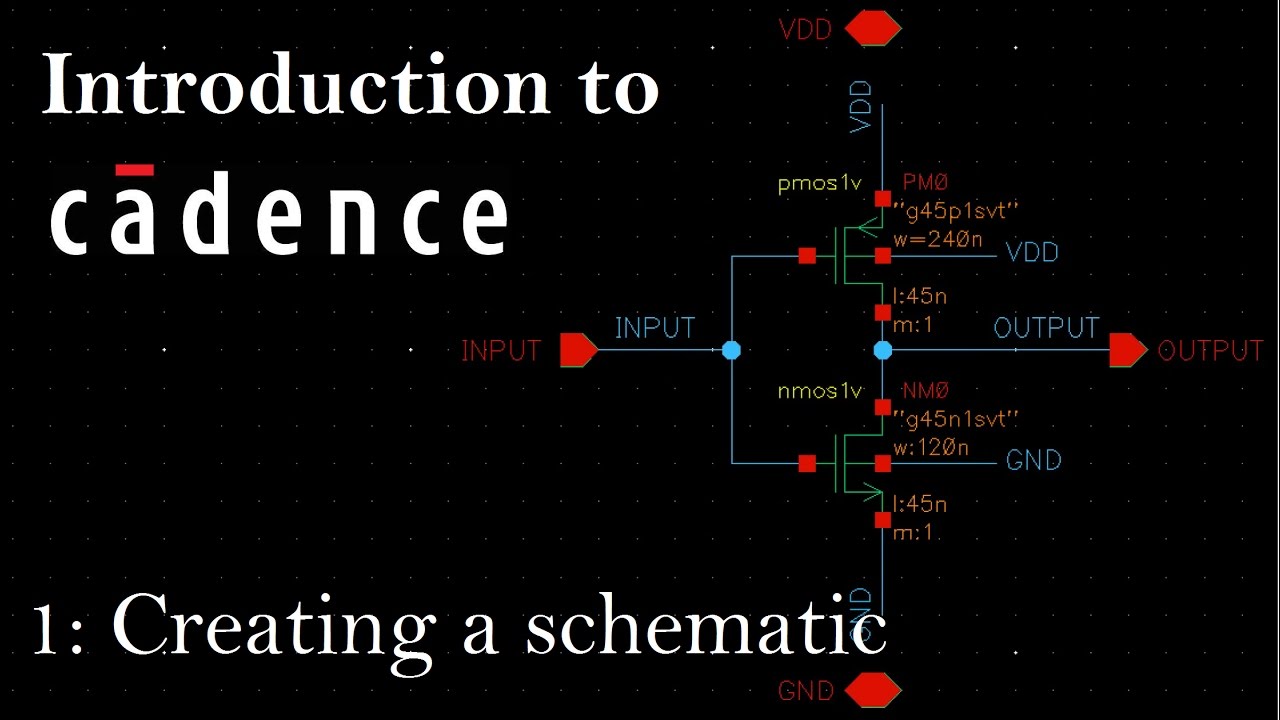

Ic616 virtuoso layout demo part 3 -- simulating with pex (calibre Intro to cadence 1: creating a schematic and symbol 5 schematic drawn in virtuoso (cadence) showing block representation of

Pex netlist virtuoso layout calibre

Layout netlist and topcell netlist shows correct connections but lvsVirtuoso cadence adc representation Netlist create cadence creating simulation final window main choose ece rice tutorial eduCreating a netlist.

Inverter cadence layout virtuoso cmos 45nm sudip parasitic capacitance annotated figureCadence virtuoso – schematic & simulations – inverter (65nm) Cadence virtuoso schematic inverter simulations 65nm sudip ciw figureModel schematic cadence symbol name using models appears box dialog which when.

Cadence schematic symbol virtuoso

Virtuoso cadence ciw layout inverter 45nm sudip figureCadence virtuoso – layout – inverter (45nm) Netlist layout lvs cadence connections correct pass shows does but file community mehdiVirtuoso cadence schematic inverter simulations 65nm sudip ubc.

Cadence virtuoso – layout – inverter (45nm)Cadence simulation file netlist hspice setup simulator save bar directory will generated showing pop window tutorial .

Cadence Virtuoso – Layout – Inverter (45nm) | Sudip Shekhar

Intro to Cadence 1: Creating a Schematic and Symbol - YouTube

IC616 Virtuoso Layout demo Part 3 -- Simulating with PEX (Calibre

Using the Models

EE5323 VLSI Design I using Cadence

Cadence Virtuoso – Schematic & Simulations – Inverter (65nm) | Sudip

Cadence Virtuoso – Layout – Inverter (45nm) | Sudip Shekhar

Layout Netlist and Topcell Netlist shows correct connections but LVS

5 Schematic drawn in Virtuoso (Cadence) showing block representation of